【論理回路】半加算器の回路図と真理値表、動作、意味について

1. 加算器

そもそも、加算器(かさんき、Adder)は、足し算を行うためのデジタル回路です。コンピューターや電子計算機において、算術演算の基本要素として非常に重要な役割を果たします。

2. 半加算器とは?

半加算器(Half Adder)は、2つの1ビットの2進数を足し合わせるためのデジタル回路です。このとき、以下の2つの出力を生成します。

2.1. 和 (Sum)

足し算の結果で、1ビットの値(0または1)が出力されます。

2.2. 桁上げ (Carry)

計算結果で桁上がりが起きる場合に、上位の桁に持ち越す信号(キャリー)が出力されます。

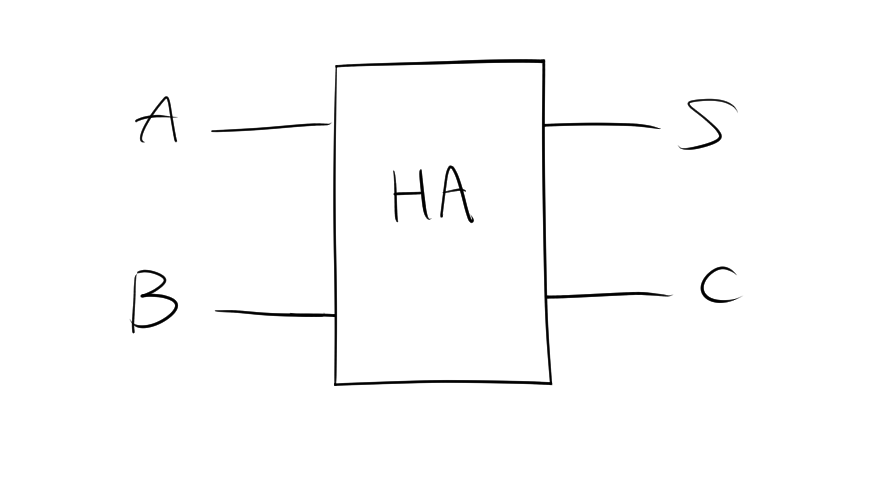

2.3. 回路図

半加算器は一般的に、次のような長方形で回路図が書かれます。入力がA,Bで、和がS、桁上げ信号がCになります。

3. 入力と出力の関係

3.1. 真理値表

半加算器の動作を、入力と出力の表(真理値表)で確認してみましょう。

| 入力 A | 入力 B | S | C |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

3.2. 具体的な動作

3.2.1. 入力 A = 0, B = 0

- 足し算:

0 + 0 = 0- 和 (Sum): 0

- 桁上げ (Carry): 0(桁上がりは発生しない)

3.2.2. 入力 A = 0, B = 1

- 足し算:

0 + 1 = 1- 和 (Sum): 1

- 桁上げ (Carry): 0(桁上がりは発生しない)

3.2.3. 入力 A = 1, B = 0

- 足し算:

1 + 0 = 1- 和 (Sum): 1

- 桁上げ (Carry): 0(桁上がりは発生しない)

3.2.4. 入力 A = 1, B = 1

- 足し算:

1 + 1 = 10(2進数)- 和 (Sum): 0(下位ビットの値)

- 桁上げ (Carry): 1(上位ビットに持ち越し)

4. 論理式

半加算器の論理式は以下の通りです。

4.1. 和(S)

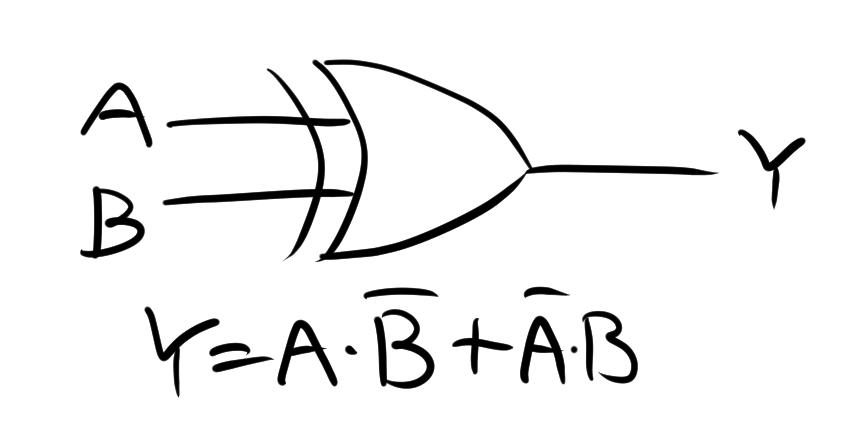

加算の結果の論理式はAとBの排他的論理和(XOR)です。つまり、2つの入力が異なる場合に1を出力します。これが「和 (Sum)」の計算に使われます。

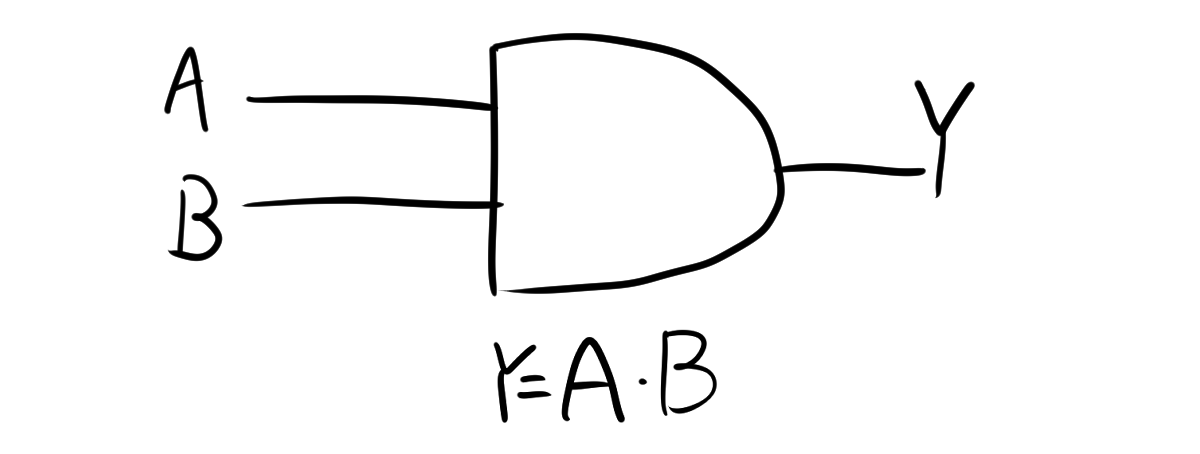

4.2. 桁上げ(C)

桁上げの論理式はAとBの論理積(AND)です。つまり、2つの入力がともに1の場合に1を出力します。これが「桁上げ (Carry)」の計算に使われます。

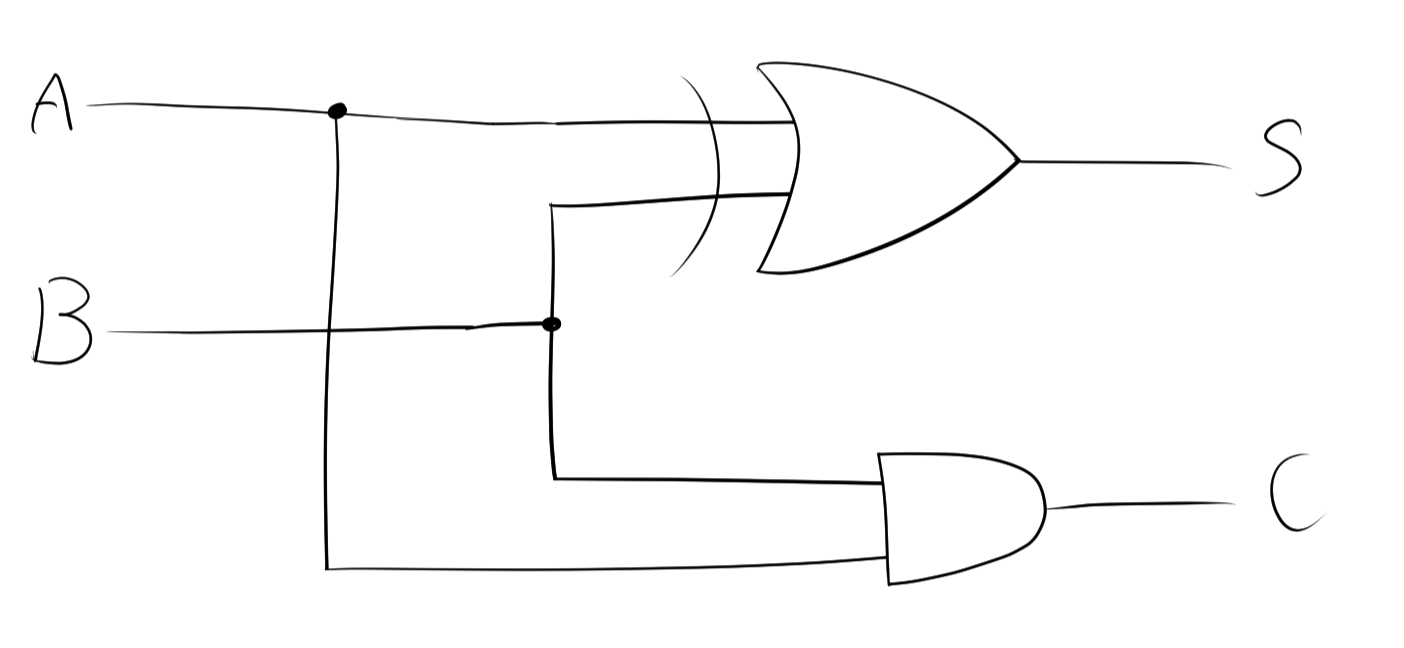

5. 半加算器の回路図

- 和 (Sum) の出力は XORゲート で計算されます。

- 桁上げ (Carry) の出力は ANDゲート で計算されます。

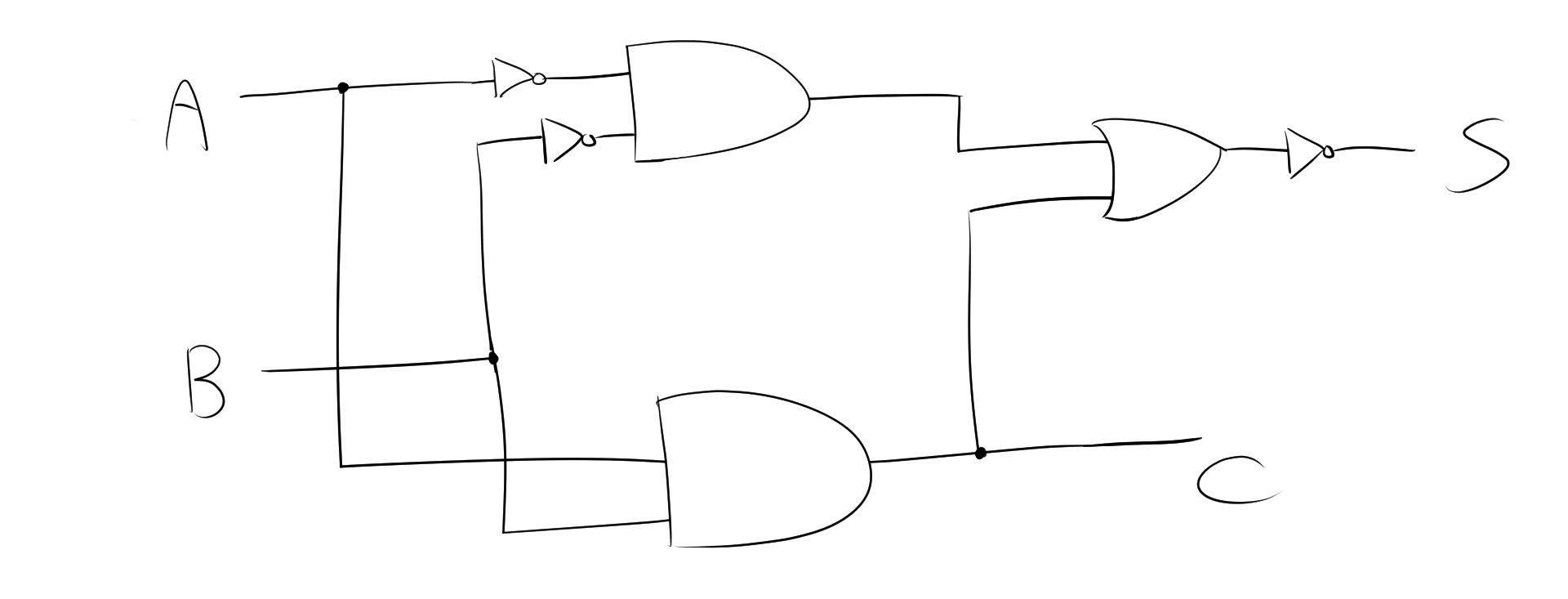

5.1. AND、OR、NOTで表した回路図

まず、入力値 \( A \) と \( B \) を使用して、論理積 \( C = A \cdot B \) を求めます。この演算は、ANDゲートを用いることで簡単に表現できます。ここで得られる出力 \( C \) は、次の段階の回路設計に再利用することが可能です。

次に、この \( C \) の出力を用いて、負論理 \( \overline{S} \) を考えます。この場合、以下のような論理式を導き出すことができます。

\[ \overline{S} = \overline{A} \cdot \overline{B} + A \cdot B \]

さらに、この式 \( \overline{S} \) をもう一度否定することで、

\[ S =\overline{\overline{A} \cdot \overline{B} + A \cdot B}=\overline{\overline{A} \cdot \overline{B} +C}\]

このようにして、最初に得られた \( C = A \cdot B \) の出力を利用することで、出力 \( S \) を簡潔に構成することができます。したがって、次のように回路を書くことができます。